Thorough verification of complex SoC platforms used for 5G wireless, IoT, and AI applications

Every innovation in architecture or IC technology puts more pressure on the functional verification process. The emerging generation of heterogeneous computing platforms is raising the bar for verification yet again. This new approach presents new challenges that must be faced by both device developers and chip users.

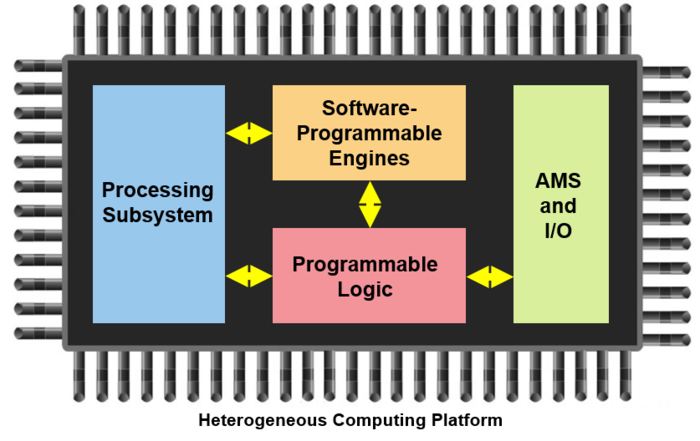

System-on-chip (SoC) designs have for some time included heterogeneous processors. Traditional CPUs have grown into multiprocessor subsystems while GPUs and other specialized compute engines have also resided on the same chip. But heterogeneous computing platforms take this architecture two steps further, by also including both FPGA-style programmable logic and software-programmable engines. These features greatly increase the flexibility available to users to implement their desired functionality in hardware, software, or a combination of both.

Heterogeneous computing platforms will be a popular and important segment of the IC industry because of their power and their adaptability for a wide range of uses. Such applications as machine learning, deep learning, and 5G wireless will benefit from the new architecture and aggressive 7nm process node. Other relevant application domains will likely include military/aerospace, autonomous vehicles, cloud computing, and the Internet-of-things (IoT). The complexity of heterogeneous computing ICs lead directly to a range of verification challenges. There are several dimensions to this problem.

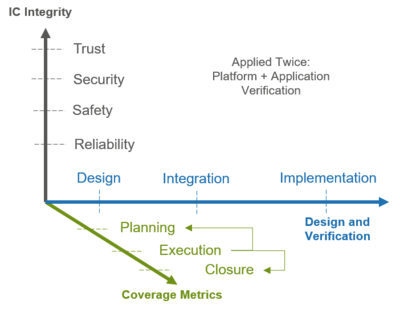

One fundamental issue is that any programmable chip must be verified twice, first by the device developer and vendor, and then by the user for a particular application. Standard ICs and traditional ASICs are verified once and then fabricated. An FPGA or SoC must be re-verified by the user in the context of the intended application for the chip. A heterogeneous computing platform has all the hardware verification complexity of an FPGA and all the hardware-software complexity of embedded computing due to the processing subsystem.

Ensuring functional reliability entails thorough verification of individual blocks, verification of block interconnections, and assurance that implementation steps preserve intended functionality. OneSpin’s Functional Reliability Solution provides numerous tools and apps, many leveraging innovative formal technologies, to span the full range of verification. Examples include the automatic checks in DV-Inspect™, the automated formal analysis of multiple apps, and the full assertion-based verification capabilities of DV-Verify™. Coverage closure can be achieved much faster with the exhaustive power of formal verification.

Additional apps are focused on full-chip integration verification, including Connectivity XL, which can verify more than a million top-level connection paths for the largest heterogeneous computing ICs. Interconnects among major subsystems are often configurable, and very complex. Once the RTL design has been fully verified, OneSpin’s EC-ASIC™ and EC-FPGA™ use formal equivalence checking to ensure that the implementation through synthesis and place-and-route does not alter design functionality.

Beyond functional correctness, many of the applications for heterogeneous computing platforms have strict safety, security, and trust requirements. OneSpin’s Functional Safety Solution verifies that hardware and software safety mechanisms work properly in the event of random faults such as alpha particle hits. This process includes the computation of hardware metrics required by safety standards for some of the key applications such as automobiles, aeronautics, and industrial equipment.

OneSpin’s Trust and Security Solution verifies that no malicious logic or hardware Trojans have been deliberately inserted during any phase of the design flow, while also detecting security vulnerabilities in the design itself. Formal technologies are ideal for this analysis, since only they can verify completeness of coverage for intended functionality and absence of any unwanted logic inserted by malicious agents or introduced due to design tool errors. The result is a fully designed, verified, and implemented IC ready for the demanding applications supported by heterogeneous computing platforms.

OneSpin’s RISC-V Integrity Verification Solution ensures that an IP core implementation does everything it's supposed to do and does not do anything it's not supposed to do. SoC designers can license a RISC-V core and be confident that it complies with the ISA specification, while IP vendors can support their own ecosystems and ensure that ecosystem partners also comply. Further, SoC designers can add custom features to the RISC-V ISA to support their specific applications. OneSpin’s Solution ensures that nothing is broken as features are added, and is flexible enough to verify new functionality.

More information…

OneSpin’s Operational SVA enables formal verification enthusiasts to develop high-level, non-overlapping assertions that capture end-to-end transactions and requirements in a concise, elegant way.

»Learn more…The OneSpin 360 Design Verification (DV) product line leverages the most advanced, high-performance formal technology as the basis for a range of verification solutions, from automated design analysis to advanced property checking.

»Download the flyer…OneSpin’s Quantify measures the quality of a formal verification test bench. It provides precise, actionable information on what parts of the design-under-test (DUT) are verified, and it highlights RTL code that could still hide bugs.

»Download the data sheet…OneSpin’s Connectivity XL App is the industry’s first and only solution for the efficient specification and formal verification of huge numbers of deep connections in multi-billion-gate chips.

»Download the data sheet…OneSpin’s VCI App enables users to export structural coverage results produced by OneSpin’s QuantifyTM in different database formats with a single command.

»Download the data sheet…OneSpin 360 DV-Verify adds coverage-driven assertion-based verification (ABV) to the DVInspect platform.

»Download the data sheet…In a systematic verification flow, requirements tracking and coverage play an indispensable role. Generally, this starts from requirements specification, where individual requirements are broken down into features, implementations, verification goals, and metrics.

»Download the data sheet…Design verification has a lot in common with human hygiene practices. The goal of both activities is to remove all dirt, grime, and bugs through an active process of establishing good hygiene.

»Download the white paper…Fault-tolerant hardware development is no longer a niche and presents new challenges. Many engineers face the daunting task of having to examine countless faulty variants of their design in order to integrate and verify multiple safety mechanisms within complex Systems-on-Chip (SoCs).

»Download the white paper…Get in touch!

Learn More About OneSpin's Hetergenous Computing Solutions!

Sven Beyer, Product Manager Design Verification