Systematic bug elimination and metrics on proper handling of random errors in the field

There is perhaps no more high-profile application of advanced ICs than autonomous vehicles. The public fascination with self-driving automobiles has led dozens of companies to pursue this field aggressively, and many of their solutions involve highly complex IC designs. Automotive applications also highlight the need for the complete spectrum of IC integrity. The requirement for functional reliability is clear; a missed systematic error (design bug) could easily result in injury or death to occupants of a vehicle or those nearby.

Automobile ICs must be able to handle random errors in actual use without compromising safety, so functional safety requirements are also high. Trust and security are equally important; the prospect of an adversary gaining control of a vehicle through an inserted hardware Trojan or exploitation of a security flaw is deeply frightening. Thus, the full range of IC integrity solutions is needed. Even those in the industry who don’t follow the technical details appreciate the huge liability risks involved.

Industrial applications, most notably nuclear power plants, have many similar characteristics to the automotive domain. There is strong motivation to eliminate systematic errors, survive random errors, and thwart adversary attacks. Another common aspect to industrial and automotive applications is the presence of established standards such as ISO 26262 for automobiles and other road vehicles, EN 50128 for railways, and IEC 61508 for industrial safety systems.

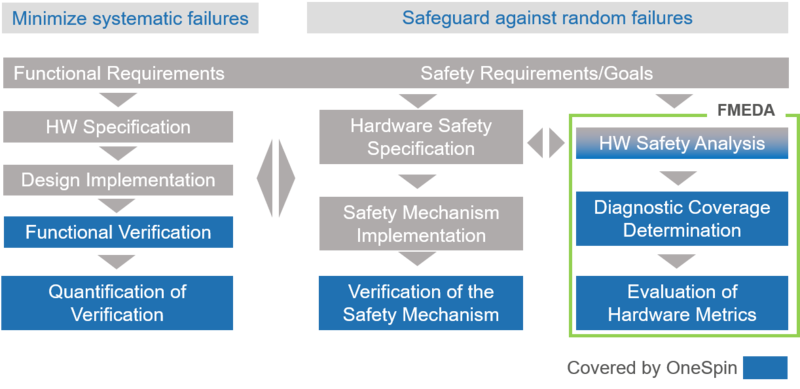

ISO 26262 is a widely cited example of a standard with precise requirements that directly drive robust IC verification flows. It divides errors into systematic errors in the design and random errors in the field. OneSpin’s Functional Reliability Solution leverages innovative formal technologies to span the full range of verification to eliminate systematic errors. The solution includes automatic checks in DV-Inspect™, automated formal analysis provided by multiple apps, and the full assertion-based verification capabilities of DV-Verify™. The exhaustive nature of formal means that it is possible to prove exhaustively that a design meets its specification.

Once the RTL design has been fully verified, OneSpin’s EC-ASIC™ and EC-FPGA™ use formal equivalence checking to ensure that the implementation through synthesis and place-and-route does not alter design functionality.

OneSpin’s Functional Safety Solution verifies that hardware and software safety mechanisms work properly in the event of random faults such as alpha particle hits. ISO 26262 defines this process in considerable detail, including the calculation of specific metrics for hardware robustness and the probability of hardware failure due to random errors (faults). These metrics can be calculated for even the largest IC designs.

ISO 26262 does not currently define security or trust requirements but, as mentioned earlier, this is an area of considerable importance. OneSpin’s Trust and Security Solution verifies that no malicious logic or hardware Trojans have been deliberately inserted during any phase of the design flow, while also detecting security vulnerabilities in the design itself. Formal technologies are ideal for this analysis, since only they can verify absence of any unwanted logic inserted by malicious agents or introduced due to design tool errors.

More information…

OneSpin’s Fault Propagation Analysis App automatically identifies non-propagatable faults, allowing their safe elimination prior to simulation, thereby cutting on simulation and debug time while increasing the nominal fault coverage.

»Learn more about the Fault Propagation Analysis App…OneSpin’s Fault Injection App automates the definition and injection of fault scenarios, eliminating the need of a separate testbench, thereby cutting on engineering effort while enabling a unified and standard-compliant formal verification flow.

»Learn more about the Fault Injection App…Fault-tolerant electronic components in safety-critical systems are now commonplace in many industry sectors, including automotive, aerospace, power generation, defense, and medical.

»Download the flyer…OneSpin 360 EC-FPGA is an automatic sequential equivalence checker that prevents field programmable gate array (FPGA) design flows from introducing synthesis, place-and-route and other implementation errors.

»Download the data sheet…OneSpin’s Connectivity XL App is the industry’s first and only solution for the efficient specification and formal verification of huge numbers of deep connections in multi-billion-gate chips.

»Download the data sheet…OneSpin’s VCI App enables users to export structural coverage results produced by OneSpin’s QuantifyTM in different database formats with a single command.

»Download the data sheet…OneSpin 360 DV-Verify adds coverage-driven assertion-based verification (ABV) to the DVInspect platform.

»Download the data sheet…In a systematic verification flow, requirements tracking and coverage play an indispensable role. Generally, this starts from requirements specification, where individual requirements are broken down into features, implementations, verification goals, and metrics.

»Download the data sheet…OneSpin’s Fault Injection App (FIA) automates the definition and handling of fault injection scenarios, removing the need for ad hoc verification flows or environments, thereby cutting on engineering effort and promoting reusability across projects and teams.

»Download the data sheet…OneSpin’s Fault Propagation Analysis (FPA) App automatically identifies non-propagatable faults, allowing their safe elimination prior to pre and post simulation, thereby cutting on simulation and debug time while increasing the nominal fault coverage.

»Download the data sheet…Functional safety standards demand that this risk be assessed and adequately minimized through tool qualification and other processes. For engineering teams, this is a time-consuming task and, worryingly, one for which there are no mature solutions yet. Tool vendors may provide safety certificates or packages, in an attempt to support their customers with safety compliance. Strategies vary and so do the benefits to the user and project.

In this paper, we review requirements on tool classification and qualification, present different safety compliance strategies, and explain their benefits to safety-critical hardware projects.

Functional safety standards require a rigorous development process to minimize the risk of introducing systematic faults. Some RTL issues may only reveal themselves as bugs in the synthesis netlist. Additionally, synthesis tools manipulate the design to map it into the fixed FPGA structure. These complex transformations present a high risk of introducing bugs. Gate-level simulation and lab testing can only cover a tiny portion of the FPGA functionality and are likely to miss implementation bugs. Moreover, they are slow to run and challenging to debug.

This white paper presents an implementation signoff flow proving that the final FPGA netlist is functionally equivalent to the RTL model. Based on FPGA-specific, mature formal verification technology, the solution is exhaustive and efficient, catching many issues before synthesis starts.

Automotive technology has come a long way since the days of the Ford Model T. Today's smart vehicles not only assist their drivers with tasks such as parking, lane management, and braking, but also function as a home away from home, with WiFi hotspots and sophisticated entertainment systems. These sophisticated features are made possible by increasingly complex electronic systems—systems that present countless new opportunities for things to go wrong. A defective headrest video screen may be an irritation to a young passenger in the back seat, but a malfunctioning corrective steering system could cost the occupants of the vehicle their lives. Adequate verification is essential.

OneSpin's formal verification solutions can help automotive suppliers continue to advance their technology while keeping drivers and passengers safe. Our safety-critical white paper examines the ISO 26262 automotive standard and makes a case for its indispensability.

Fault-tolerant hardware development is no longer a niche and presents new challenges. Many engineers face the daunting task of having to examine countless faulty variants of their design in order to integrate and verify multiple safety mechanisms within complex Systems-on-Chip (SoCs).

This white paper examines key goals and challenges in fault-tolerant hardware verification, and presents formal solutions that ensure predictable hardware behavior under all relevant operating conditions and fault scenarios, while saving in engineering and computational resources.

This presentation focuses on the formal verification solutions that can provide high ROI in AEH development projects. These solutions reduce the risk of undetected hardware issues, and enable a more predictable and efficient path to airworthiness certification.

»Watch the video on YouTube…We check the web for relevant safety-critical news content and link directly to the source from here. Want to get your monthly recap of relevant news?

»Sign-up to our newsletter…"Our verification approach is based on the verification methodology of [1,2], which is marketed under the name GapFreeVerification™ by OneSpin Solutions1 . This approach uses so called operational properties to construct complete formal specifications and includes methods to verify specification completeness."

"For portability and accessibility, we store tabular specifications in a standard spreadsheet format. The automatic translators of the tabular representation are implemented using Java Emitter Templates (JET) [5]. The operational properties 7 of core functionality are expressed in SystemVerilog assertions using Timing Diagram Assertion Library (TIDAL™) [13]. The properties of auxiliary clusters are written in plain SystemVerilog assertions. Design verification and completeness checks are performed with OneSpin 360 Design Verifier."

“The MicroSemi ProASIC3 FPGA is a core component of the Advanced Logic System (ALS), and use of the OneSpin 360 Equivalence Checker is an integral part of our FPGA development process for nuclear safety systems.” says Erik Matusek, Safety System Platform Manager at Westinghouse Electric Company, LLC

»Read the full article…Get in touch!

Learn more about OneSpin's Automotive and Industrial Solutions!

Jörg Grosse, Product Manager Functional Safety