Real Highlights for Virtual DAC 2020

By Sergio Marchese, OneSpin Solutions

As the 57th edition of the Design Automation Conference goes online, learning about the latest, most efficient IC integrity assurance solutions is easier than ever

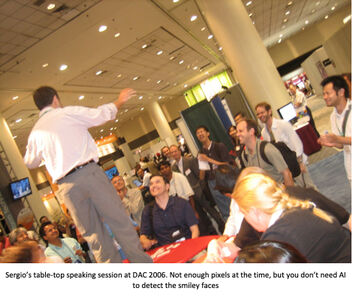

My first time at DAC was in 2006 in San Francisco. I was mesmerized by it: so many people, so much cool technology, so much fun with weird giveaways, raffles, happy hours, the Denali party and Disco Inferno at the legendary Fillmore!

DAC is the most important, comprehensive conference for anyone developing integrated circuits (ICs) and systems-on-chips (SoCs). With an incredible list of events, including workshops, tutorials, keynotes, and panels, there is plenty to choose from. Everyone who is anyone in the electronic design automation (EDA) industry is present on the exhibition floor, offering engaging presentations and demos of their products and solutions. There is a vast research program with papers from top academic institutions. Despite significant cuts in travel costs in recent years, all major IP and silicon providers, and many small and medium-sized companies, make sure that they have at least a few engineers attending. As chip complexity continues to increase exponentially, design automation is critical to developing high‑integrity silicon at a lower cost. Nobody can afford to stay behind. And if that is not enough, let’s be honest: talented and bright engineers are attracted by companies that give them access to the best tools and design solutions.

Due to the COVID-19 pandemic, the 57th edition of DAC (July 20-24, 2020) will be the first virtual one. Hopefully, it will also be the last one held during a health emergency. As it is not possible to virtualize the atmosphere at the Fillmore, there is no doubt that the fun part of the conference will be significantly affected. Nevertheless, virtual DAC 2020 is poised to be a success and an opportunity to improve the conference format for years to come. Registration rates start at $0, and $49 gives access to all content except the research program and the tutorials. Most content, including videos of the oral sessions and posters, will be available online for the whole duration of the conference, and afterward until August 1. Attendees will be able to ask questions to speakers through a live text chat or book 1:1 meetings. Engineers everywhere have a unique opportunity to learn about the most advanced design automation solutions from the comfort of their homes and offices and at their own pace.

The best ways to explore the conference program are through its search interface and by scanning the daily event matrix. Here, I want to highlight a selection of events focusing on IC integrity solutions where OneSpin is involved.

FMEDA for Automotive ISO 26262

Quantitative FMEDA for automotive applications and compliance with ISO 26262 can be challenging. Fault injection can be used for deriving hardware safety metrics. However, for complex chips or semiconductor IPs with a variety of safety mechanisms, using fault simulation is laborious and time-consuming. What are the right stimuli to use? How can I speed up fault simulation? How can I detect early in the flow if the safety architecture will not get me to the target SPFM and LFM metrics, whether my goal is an ASIL-B, ASIL-C, or ASIL-D system? The good news is that there are alternative ways to approach the problem that can reduce or even eliminate the need for fault simulation. Learn more about how to implement a streamlined, automated, and efficient quantitative FMEDA flow with Jörg Grosse at the Designer Embedded and IP Track Poster session (126.34) on Tuesday, July 21, from 7:30 a.m. to 8:30 a.m. PST, or send Jörg an email.

FPGAs for Nuclear I&C

The IEC SC 45A standard series regulates electronic instrumentation and control equipment in nuclear applications. In particular, IEC 62566 focuses on FPGA development activities, including verification of the post-synthesis and post-place-and-route netlists. How can you reduce the need for slow gate-level simulations? How can you be sure that the implementation tools have not introduced errors? Is that possible when using more advanced implementation flows? Luckily, there are formal verification tools that are dedicated to FPGA flows. Within a few days of effort, it is possible to exhaustive verify large netlists. Crucially, these tools are independent of the implementation tools, an essential requirement from safety standards. Learn more with Jürgen Dennerlein from Framatome at the Designer Embedded and IP Track Poster session (126.83) on Tuesday, July 21, from 7:30 a.m. to 8:30 a.m. PST.

Automated Trust and Assurance of IPs

Developers of safety- and security-critical SoCs can no longer afford to ignore the risks of security vulnerabilities when integrating third-party IPs. Re-verification of an IP is not feasible, and the cost is prohibitive, even more so when the implementation-level expertise is not in-house. Verification and code reviews are likely to miss stealthy Trojans or vulnerabilities that surface in deep corner-case, misuse scenarios that are far from the intended usage of the IP. Some solutions are emerging to address these challenges. The Aerospace Corporation and OneSpin will share results of the application of an automated IP trust and assurance flow on over 90 RTL designs. Learn more with John Hallman at the Trends in Meeting IP Challenges for a New Decade session (19.2) on Thursday, July 23, at 1:30 p.m. PST or send John an email.

RISC-V Security and Assurance

RISC-V has reinvigorated the open-source hardware community. Many individuals, companies, and organizations, including the OpenHW Group, are continuously releasing new and updated implementations of the RISC-V ISA. However, thorough functional verification of processors is very costly. Established IP providers using proprietary architectures have decades of experience and enormous resources dedicated to functional verification. And yet, security issues are routinely missed. RISC-V makes it possible and affordable to take the assurance and security verification of processor cores to the next level, matching or even exceeding the quality of established IP providers. Edaptive Computing and OneSpin will share results of the application of a RISC-V formal verification solution to two cores (RocketCore and OpenHW CV32E40P). Learn more with Sven Beyer at the Designer Embedded and IP Track Poster session (126.53) on Tuesday, July 21, from 7:30 a.m. to 8:30 a.m. PST, or send Sven an email.

RISC-V Ecosystem

Leaders in the RISC-V ecosystem have a dedicated DAC 2020 event: the RISC-V Theater. The companies presenting include Andes, Imperas, Microchip, OneSpin, and UltraSoC. OneSpin will present its RISC-V Integrity Verification Solution and share the results of formal verification of RISC-V cores and SoCs. Learn more with Salaheddin Hetalani in the RISC-V Theater on Tuesday, July 21, at 11:30 AM. PST or send Salaheddin an email.

Processor Side-Channels

Hardware security weaknesses and vulnerabilities are leveraged in ever more exploits. Since the discovery of Meltdown and Spectre in early 2018, micro-architectural side-channels and transient execution attacks have become a gold mine for security researchers and, possibly, hackers. While there are no systematic processes and tools that address this risk comprehensively, research efforts are showing promising results. The Unique Program Execution Checking (UPEC) method introduced in this paper is based on formal methods. The paper demonstrates that it is possible to analyze a processor RTL implementation and systematically detect vulnerabilities that can derive from the processor microarchitecture and even from minor implementation choices. In the DAC 2020 paper authored by staff at the University of Kaiserslautern, Germany, Stanford University, California, and OneSpin, and titled “A Formal Approach for Detecting Vulnerabilities to Transient Execution Attacks in Out-Of-Order Processors,” the authors extend their previous work on UPEC to more complex, out-of-order processors. Learn more at the Trust...but Securely Verify research session (87.3) on Friday, July 24, at 2:00 p.m. PST or send Raik an email.

Virtual Exhibits

The conference’s exhibit hours are July 20–22, from 10:30 a.m. to 1:30 p.m. PST. Many of the best EDA companies in the world will be available to show their latest technology and share expertise on how to tackle the hardest IC design and verification challenges. OneSpin’s awesome AE team will be happy to show tool demos on functional correctness, safety, and trust and security. You will be welcome to ask questions on the sessions above, on topics such as formal signoff, formal structural, functional, and model-based mutation coverage, verification of floating point units (FPUs), automated connectivity checking for large SoCs, protocol verification with ABVIPs, or on any pressing verification topic you might have.

Don’t miss DAC 2020

OneSpin’s experts will be at hand during the entire conference and beyond. Whether you are an engineer working in a big or small company, a student, an academic researcher, or a freelance consultant, don’t hesitate to get in touch. We will do our best to respond to all your questions and requests for consultation on specific topics and 1:1 demos. Please register your interest and book a meeting now at onespin.com/dac—it’s free! Most important of all: Enjoy virtual DAC 2020!