Connectivity specification and verification for multi-billion-gate chips

Modern, 7nm ASIC and FPGA SoCs include hundreds of thousands of IP and module instances, and complex pin multiplexing logic. Connection paths may involve thousands of signals. Engineers often need to specify and verify in excess of one million connections. Moreover, maintaining a connectivity specification through design revisions and derivative projects require excessive effort. Overall, this is a time-consuming, error-prone task not adequately supported by simulation-based techniques or traditional formal connectivity checking apps.

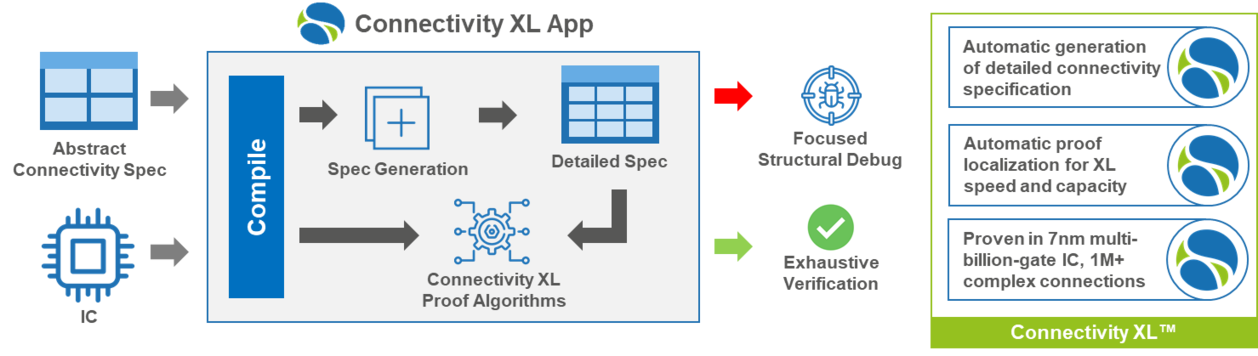

OneSpin’s Connectivity XL App is the industry’s first and only solution for the efficient specification and formal verification of huge numbers of deep connections in multi-billion-gate chips.

OneSpin’s Connectivity XL App addresses both the specification and verification challenges. The user can create and maintain an abstract, compact connectivity specification leveraging IP and module integration rules, naming conventions, wildcards, and global multiplexing conditions. The app automatically generates the detailed connectivity specification table. Crucially, delays, inversions of polarity, and full paths for source, destination, and multiplexing signals are automatically generated. This results in a dramatic reduction in engineering effort. Failures can be debugged easily as the app reports localized path information that pinpoints the connection break point.

Get in touch!

Try out OneSpin's Connectivity XL App for large volume verification challenges