Verification Knowledge at Your Fingertips

By: Rob van Blommestein

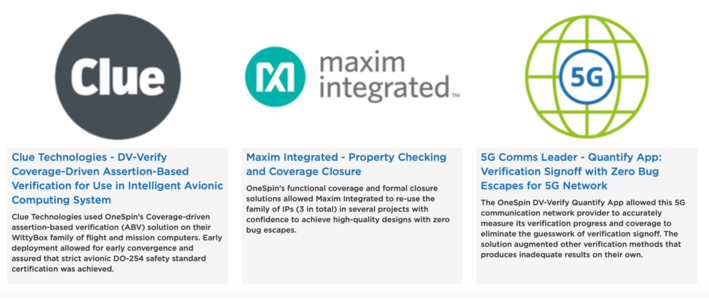

Leading Companies Share What They've Done

If you’re like most engineers, you’re curious about how other engineers tackle some of the most difficult challenges. What can you absorb from them and apply to your own projects? Learning from experience has tremendous value but learning from others’ experiences is arguably more valuable since the cost to acquire that knowledge is significantly cheaper.

At OneSpin, we’ve lowered the cost of that knowledge for the verification community. Our newly launched Case Study Library is full of examples of best practices for achieving IC integrity. You’ll find stories from a variety of companies and industries spanning a myriad of applications including:

- Clue Technologies talking about their use of coverage-driven assertion-based verification,

- Maxim Integrated discussing property checking and coverage closure,

- Xilinx covering FPGA and safety verification,

- Bosch addressing automotive DSP verification

- A prominent 5G networking company showing how verification signoff was achieved with zero bug escapes

- A telecom leader providing a tour of functional coverage and formal closure

- An edge computing customer talking about the use of dead code analysis for first pass detection

- A nuclear powerplant company examining how to achieve safety and security assurance

- A leader in datacenter technology explaining how to accelerate verification

These case studies along with others can be downloaded at https://onespin.com/customer-stories.

We’ve also given our users a chance to spotlight their achievements as part of our Osmosis user group event. This year’s virtual event featured presentations from ICsense, Infineon, Sandia National Laboratories, and Nokia.

ICsense talked about the use of formal consistency checks as a means of reducing overall verification effort and engineering resources. Creating the framework for designers to quickly check their designs before simulation is essential as is the use of waivers that are not prone to code changes.

Infineon highlighted how formal verification was deployed to exhaustively verify designs that implement safety mechanisms such as Error Correction Codes (ECCs). These ECC designs that encode a large data vector and detect multiple bit errors have been traditionally verified with simulation-based methods even though they are better suited for formal verification.

Sandia explored the topic of how much verification is enough when it comes to formal. When do you know when to stop writing additional properties? How can you achieve confidence that enough properties have been checked to verify correctness of the design?

Nokia provided semi-formal techniques for large counter verification that go beyond counter abstraction. Verifying the actual counters themselves made counter abstraction techniques inadequate because the techniques would alter the design being verified. The semi-formal methods that were used helped to successfully verify the large counter corner cases throughout the full range of operation.

These presentations along with the technical deep dives from OneSpin experts on the topics of functional correctness, FMEDA automation and safety, trust and security, RISC-V, and FPGA equivalence checking can be viewed on our web site at https://onespin.com/resources/videos/osmosis-2020.

Knowledge and experience are vital to achieving IC integrity success. We’re happy to provide the community with the means to share their knowledge to assure that designs operate as intended, are safe, trusted, and secure.